发布日期:2022-04-17 点击率:71

【导读】大家如果心细的话应该会留意到本期文章的题目,串扰案例分解,已经可以揭示上期问题的答案了,主要是串扰在作怪,原来如此,是不是恍然大悟?

继续来找茬——DDR2设计案例分享(连载1)

http://www.cntronics.com/gptech-art/80029463

大家来找茬——任性的DDR2设计(下)

http://www.cntronics.com/cp-art/80029257

大家来找茬——任性的DDR2设计(上)

http://www.cntronics.com/sensor-art/80029217

从截图可以看到,本设计的问题主要有3点:

1、叠层设计不合理,信号与信号之间的间距比信号到参考的间距还小;

2、双内层走线没有避免平行走线的问题,而且能避开的区域也没有意识去避开,以上两点造成的直接影响就是串扰很大;

3、板子本身比较厚,这样靠近表层的信号势必Stub很长,影响阻抗及回损。

解决该串扰最直接有效的方法是优化叠层,尤其是这种过多个连接器的背板设计。

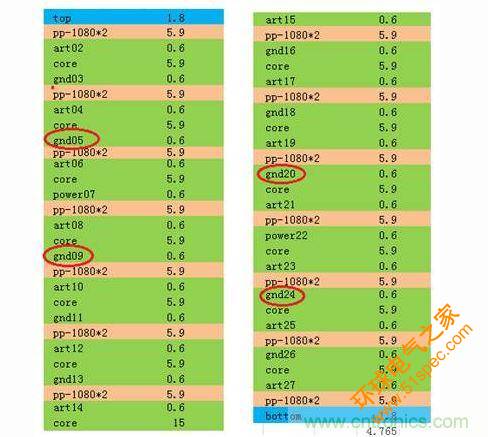

要想完全消除串扰影响,最好就是加参考层,能一层信号一层参考是最好不过的,这也是多数背板的叠层设计方案,当然,成本会有一定的增加。优化后的叠层如下图一所示。

图一 优化后的叠层

上面的解释用仿真其实也是可以验证的。

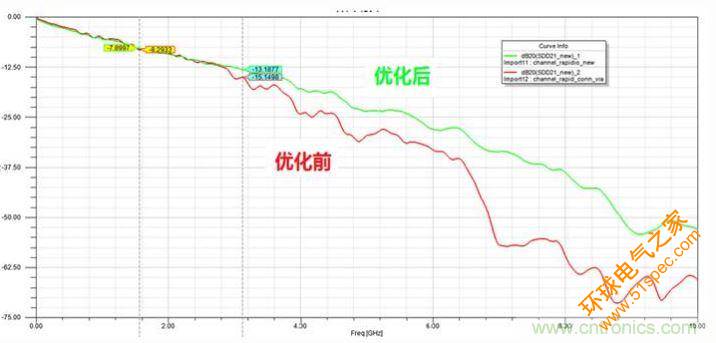

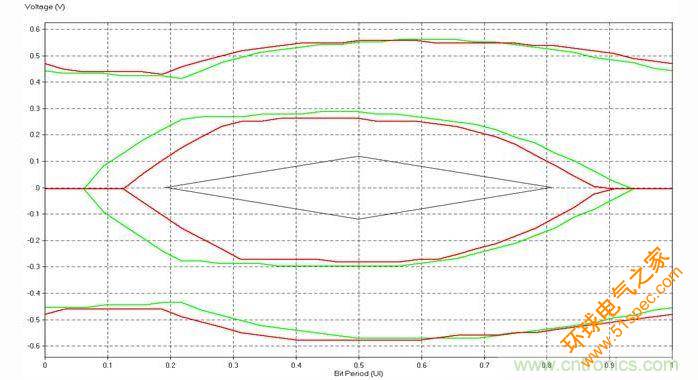

另外对过孔也进行一定的背钻等优化处理,分别提取优化前后单对通道(不考虑串扰)和多对通道的模型(考虑串扰),然后进行通道无源及有源眼图仿真,单通道的仿真结果对比如下图二和图三所示。

图二 优化前后通道插损对比

图三 优化前后通道眼图对比

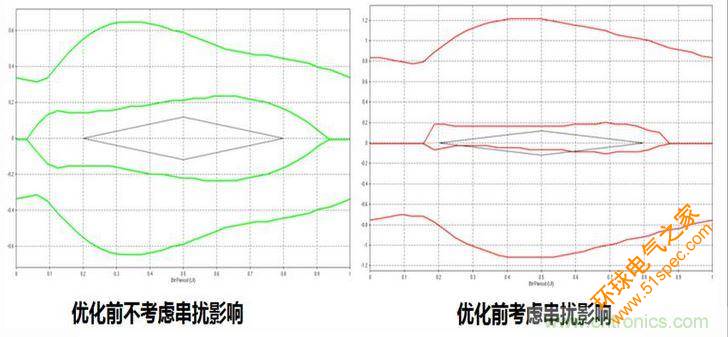

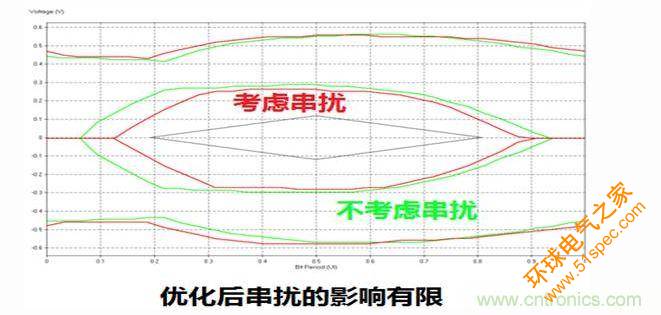

从以上单通道的仿真也可以说明,优化前虽然性能会差一点,但如果不考虑串扰的话单通道眼图还是满足要求的,这也可以解释插几个槽位还是可以工作的。我们再来仿真下考虑串扰的情况,仿真对比如下图四所示。

图四 优化前后考虑串扰的眼图对比

从图四可以看出,一旦考虑串扰,也就是多个插槽同时工作的时候,原始设计的背板因为串扰的原因眼图已经不满足要求了,而经过优化后即使考虑串扰,也就是多个插槽同时工作都不会对眼图有太大的影响,眼图照样满足要求,也就是系统照样正常工作。

经过后期的实际测试,此背板问题最终得到了解决。

下一篇: PLC、DCS、FCS三大控

上一篇: 专家教你:算一算传输