当前位置: 首页 > 工业电子产品 > 集成电路(ICs) > 电源管理芯片PMIC > 栅极驱动器

发布日期:2022-07-20 点击率:60

【导读】高速栅极驱动器可以通过降低FET的体二极管功耗来提高效率。本文主要来讨论过高速栅极驱动器如何帮助系统实现更高的效率。

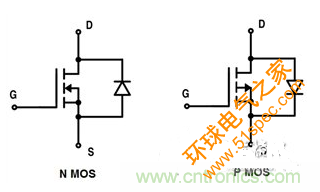

高速栅极驱动器可以通过降低FET的体二极管功耗来提高效率。体二极管是寄生二极管,大多数类型的FET固有。它由p-n结点形成并且位于漏极和源极之间。图1所示为典型MOSFET电路符号中表示的体二极管。

图1:MOSFET符号包括固有的体二极管

限制体二极管的导通时间将进而降低其两端所消耗的功率。这是因为当MOSFET处于导通状态时,体二极管上的压降通常高于MOSFET两端的电压。对于相同的电流水平,P = I&TImes;V(其中P是功耗,I是电流,V是电压降),通过MOSFET通道的传导损耗显著低于通过体二极管的传导损耗。

这些概念在电力电子电路的同步整流中发挥作用。同步整流通过用诸如功率MOSFET的有源控制器件代替二极管来提高电路的效率。减少体二极管导通可以使这种技术的优点最大化。

下面考虑同步降压转换器的情况。当高侧FET关断并且电感器中仍然存在电流时,低侧FET的体二极管变为正向偏置。死区时间短对避免直通很有必要。在此之后,低侧FET导通并开始通过其通道导通。相同的原理适用于通常在DC / DC电源和电动机驱动设计中发现的其它同步半桥配置。

对于高速接通,栅极驱动器的一个重要参数是导通传播延迟。这是在栅极驱动器的输入端施加信号到输出开始变高时的时间。这种情况如图2所示。当FET重新导通时,体二极管将关断。快速的导通传播延迟可以更快地导通FET,从而最小化体二极管的导通时间,进而使损耗最小化。

图2:时间示意图,t_PDLH是导通传播延迟

TI的产品组合包括具有行业领先的高速导通传播延迟的栅极驱动器。参见表1。

表1:高速驱动器

系统效率是一个团队努力的结果。本博客系列介绍了高速和高电流栅极驱动器是关键件。立即访问www.TI.com/gatedrivers开始设计您的高效系统。

其他信息

· TI Designs参考设计库中展示了高效率系统中的高速栅极驱动器:

· “隔离GaN驱动器参考设计”。

· “用于电信的1 kW三路隔离DC / DC数字电源(-8V @ .25A)”。

下一篇: PLC、DCS、FCS三大控

上一篇: 使用超声波装置如何实