发布日期:2022-04-22 点击率:45

引言

超高速集成电路硬件描述语言(VHDL)是一种用于电路设计的高级语言,与其他硬件描述语言相比,其具有语言简洁、灵活性强、不依赖于器件设计等特点,使其成为EDA技术通用的硬件描述语言,使EDA技术更便于设计者掌握[1]。

本文依托QuartusⅡ软件环境,采用VHDL语言编程,在不修改标准时钟电路的基础上,通过软件编程设计了一款能够将用户作息时间在标准时钟电路中进行提醒的作息时间控制器,该作息时间控制器实现了不同作息事件不同提醒程度和方式的设计目的。

1设计原理

一款根据作息时间的不同,通过不同程度和方式提醒的作息时间控制器,其提醒和模式设计是整个设计的核心。本文充分运用VHDL语言"自顶向下"的设计优点,将整个系统进行模块划分,设计每一个模块的功能及各模块之间的接口,最终确定分为四大模块:分频模块、时间调整模块、计数器模块以及显示模块。

2功能模块

2.1分频模块

该模块负责输入时钟信号,因为该ⅡFРA中已有的时钟信号是50>HM的时钟信号,所以该分频器是一个50M分频的分频器,以保证通过这个分频器后每一个输入信号是1S,从而使后面的计时器每一次计数为1S,保证计数的准确。其Symbol如图1所示,其中clk为系统时钟信号输入端,larrz为1HM时钟频率输出端。

图11Hz分频器symbol

2.2时间调整模块

该模块负责实现计时器的预设功能,通过手动输入信号,在计时之初就改变计时器的初始计时状态。计时器的最大计时时间是固定的,即23h59min59S,同时可以手动校正与标准时钟的误差。调整电路设计如图2所示,该模块是由一个非门和一个二选一或门组成的,其中非门的作用是将输入的低电压转化为高电压,二选一或门的作用是保证标准时钟电路正常进行的情况下,通过手动也能对时钟电路进行控制。

2.3计数器模块

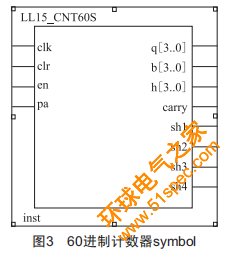

该模块把分频器模块输出的信号作为相应信号,每有一个信号则作用一次,并在这个计时器模块中加入了暂停和清零两个信号的端口,用另外两个可自由控制的开关给定信号,来控制暂停和清零功能的动作与否[4]。同时为了完成最大计时为23h59min59s,这个计数器模块由3个计数器组成,2个60计数器用来统计秒位和分位的时间变化,1个24计数器用来统计时位的时间变化。其中60秒位计时器的输入端链接60分位计时器的输出端,保证每60s显示1min,60分位计时器的输入端链接24时位计时器的输出端,保证每60min显示1h,这样设计可以保证计时器的计时规律与实际计时规律相同,更直观。

60进制计数器其symbo1如图3所示,引脚c1k是接受从60秒位计时器中来的进位信号,并把这个时钟信号导入到模块中,即实际中计时60s记为1min:引脚c1r是控制清零功能的,当系统收到从这个端口进入的信号时,此计数器模块内的所有计时结果清零:引脚en是控制暂停功能的,当系统收到从这个端口进入的信号时,此计时器不管c1k口是否有信号,系统均保持计时不变,保持当前状态:引脚pa为接受改变亮灯模式的输入信号:引脚h[3..o]是输出亮灯模式的类型的信号:引脚q[3..o]是输出计时个位的结果信号,能显示0到9:引脚b[3..0]是输出计时十位的结果信号,能显示0到6:引脚carry是输出进位信号,当此计数器达到最大值即60时,系统则输出一个进位信号,同时系统计时结果清零。引脚sh1、sh2、sh3、sh4是在达到作息时间表中时间时向彩灯输出信号,达到闹钟设定秒、分钟位效果。

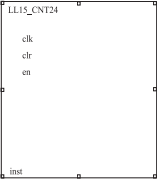

24进制计数器其symbo1如图4所示,引脚c1k、c1r、en与60进制计数器功能相同。引脚q[3..o]是输出计时个位的结果信号,能显示0到9:引脚b[3..0]是输出计时十位的结果信号,能显示0到9:引脚carry是输出进位信号,当此计数器达到最大值即24时,系统则输出一个进位信号,同时系统计时结果清零。引脚sh1、sh2、sh3是在达到作息时间表时间时向彩灯输出信号,达到闹钟控制时位的效果。

2.4显示模块

该模块用来处理计数器模块的输出信号,通过相应的编码把计时结果显示在7位LED数码管上,从而使计时结果能够直观显示出来[5]。其symbo1如图5所示,引脚d[3..0]是接受从计时器模块输出的信号,每一个显示模块与一位计时器输出信号相对应:引脚h[6..0]是把处理后的计时器输出信号编译到7位LED数码管上,使得每一位数字能够显示出来。

图424进制时计数器symbol

图5显示模块symbol

3结语

本文利用VHDL语言,在Quartus一软件环境下进行编程设计的作息时间控制器,当下载到DE2-115开发板上进行硬件验证,所得结果满足设计要求。

在设计过程中,发现作息时间控制器与我们日常所用的闹钟等提醒器件相近,但该作息时间控制器无法与闹钟一样可以让用户自己设定提醒时间,希望能与读者共同探讨是否能将作息时间表的设定交予用户设定的合理方案。

下一篇: PLC、DCS、FCS三大控

上一篇: 基于PLC的四轴运动控