当前位置: 首页 > 工业电子产品 > 其他电子产品 > 开发板,套件,编程器 > 开发板

发布日期:2022-10-14 点击率:61

这是我在2012年5月为客户编写的设计方案,是一种宽带无线数传方案,本质就是用软件无线电平台去实现WiFi的物理层及MAC层。在我编写这份方案的时候,还没有AD936x,Xilinx Z7000这类芯片,所以产品架构比较复杂。本方案是基于FPGA的高性能无线数据收发系统,基于WiFi技术,可实现多终端同时与基站进行通信,可稳定工作于-40~85℃,具有较高的EMC指标,可稳定工作于各种苛刻的环境。

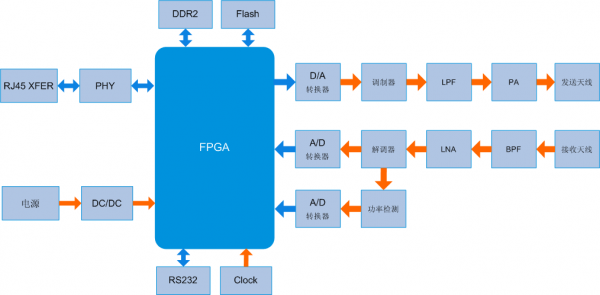

硬件设计框图

根据客户的基本技术指标,我们提出了下图所示硬件系统架构。

根据客户的描述,本产品主要用于多个视频源同时通过无线的方式向基站发送数据,需要采用较小的信道带宽和OFDM 调制方式,同时基站需要能够识别视频源。根据调研,目前市面上找不到能够真正支持非20MHz信道带宽的WiFi收发芯片,而且产品最终的工作频率为300-500MHz,无需考虑兼容WiFi 协议,因此我们参照WiFi芯片的内部结构,提出了上述的硬件设计框图。

FPGA通过GMII接口与以太网PHY芯片连接,实现一个千兆以太网口。发送数据时,FPGA内部将数据进行转换,打包,并将处理后的数据流进行串并转换,快速反傅里叶变换,最终送至外部的D/A,上变频,功率放大,然后发送出去;接收数据时,天线感应到的射频信号首先通过带通滤波器,然后送至低噪声放大器,进行解调,然后将I/Q信号送至A/D转换器,最终,FPGA通过一个逆过程将数据还原。

FPGA的选型

FPGA初步采用Xilinx Virtex-II系列实现。

Xilinx公司推出的Virtex-II解决方案为两个技术挑战性非常强的数字系统提供了很好的支持:数据通信和数字信号处理(DSP)系统。高逻辑集成度、宽总线上的快速复杂的布线、大面积的pipeline和FIFO存储需求共同组成了系统的特点。在前几代FPGA开发的基础上,Virtex-II的结构是经过高密度和高性能逻辑设计优化的。它由输入/输出模块(IOBs)和内部可配置模块(CLBs)组成。

它采用8层金属的0.15um工艺的CMOS技术,1.5V核心电源电压,专用的3.3V辅助和I/O电源电压,其系统门数从40K到8M,内部时钟速率可达420MHz,可选择配置为多种接口标准,内部含有丰富的布线资源,其SelectRAMTM结构可灵活地配置为SRAM、DRAM、CAM等多种形式的存储单元。Virtex-II系列FPGA含有极其丰富的I/O资源,可编程I/O模块为管脚和内部可配置逻辑提供接口,它支持多数流行且先进的I/O标准,I/O速率可达840+Mb/s。

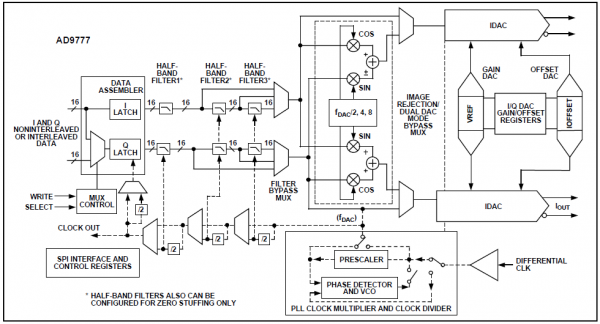

D/A转换器的选型

D/A转换器采用ADI公司的AD9777,这是一颗高速、双通道插值转换器,其提供16位分辨率,最大输入数据速率为160 MSPS(无插值),最大DAC更新速率为400 MSPS(8x插值)。该系列器件具有可选插值率(2x/4x/8x)以及能够以Fs/2、Fs/4或Fs/8混频的复合调制器。所有配置均通过一个易于使用的三线式或四线式SPI接口完成。

与外部正交调制器(例如AD8345/AD8346/AD8349)配合使用时,AD977X利用其内部复合(I&Q)混频器,就可以实现更传统的基带I/Q架构或镜像抑制上变频架构。后一架构可能非常适合那些要求高调制精度(即64 QAM)的应用,数字调制本身就能提供这种高精度。这种架构还有一个额外的优势,即可以抑制模拟混频操作固有的镜像,从而可以减少滤波级的数量,降低实现3G和宽带频谱发射所需硬件的成本。用户可通过SPI端口进行增益与失调校正,相应地改善边带抑制与LO馈通。在直接中频模式下,可以对高于70 MHz的中频(IF)进行合成。

AD9777的内部功能框图如下图所示

A/D转换器的选型

A/D转换器采用ADI公司的AD9248,AD9248是一款双核、3V、14位、20/40/65 MSPS模数转换器(ADC),集成了两个高性能采样保持放大器和一个基准电压源。它采用多级差分流水线架构,内置输出纠错逻辑,在最高65 MSPS数据速率时可提供14位精度,并保证在整个工作温度范围内无失码。

利用宽带宽、差分采样保持放大器(SHA),用户可以选择包括单端应用在内的各种输入范围和偏移。该器件适用于各种应用,包括在连续通道中切换满量程电平的多路复用系统,以及采用远超过Nyquist速率的频率对输入进行采样。AD9248适用于通信、成像和医疗超声等应用。

AD9248的内部功能框图如下图所示。

正交调制器的选型

正交调制器选用ADI公司的AD8345,AD8345是一款硅RFIC正交调制器,设计用于140 MHz至1000 MHz频率范围。该器件提供极低的本底噪声和高输出功率,可明显改善输出动态范围。它需要一个低LO驱动电平,提供额定50 Ω缓冲输出。

该器件可提供出色的振幅和相位平衡以及边带抑制特性,支持高阶/高容量QAM调制无线电。

正交解调器

正交解调器选用ADI公司的AD8348,AD8348是一款宽带正交解调器,集成有中频(IF)可变增益放大器(VGA)和基带放大器,适用于通信接收机,可进行从中频直接到基带频率的正交解调。其输入频率范围为50-1000MHz,可以很好的满足本产品的要求。

详细硬件设计框图

识别多个视频源的方法

视频源通过以太网口与发送端连接,参考TCP/IP协议,我们为每个发送端设置唯一的MAC地址,同样,基站也会有一个唯一的MAC地址,发送端将数据发送至基站时,会在报文中包含源MAC地址与目标MAC地址,这样,基站就可以分辨出不同的视频源。

PCF MAC

无线局域网(WLAN)中MAC所对应的标准为IEEE 802.11,IEEE 802.11 MAC综合了两种工作方式: 分布控制(DCF)和中心控制(PCF)两种工作方式:

分布控制方式(DCF),类似CDMA/CD,利用载波监听机制,适用于分布式网络,传输具有突发性和随机性的普通分组数据, 支持无竞争型实时业务及竞争型非实时业务。

中心控制方式(PCF),建立在DCF工作方式之上并且仅支持竞争型非实时业务,适用于具备中央控制器的网络。

PCF(Point Coordination Function)机制基于轮询机制,可以用于支持无竞争型实时业务。

考虑到该产品主要用于无线视频传输,且无需考虑兼容WiFi协议,我们决定采用PCF的方式进行数据传输。

PCF工作过程

希望发送数据的终端首先向基站发送连接请求帧,并在帧的功能性能字段的CF-Pollable(可轮询CF)子字段中表明希望加入轮询表。在收到基站的ACK信息以后,终端被列入轮询列表。轮询列表中的主机按连接标识(Association ID:AID )升序排列。AID是由基站分配的16bit标识符。

基站发出Beacon帧表明CFP期间的开始。然后基站依次向轮询列表中的终端;如果在PIFS时间间隔内没有响应,则表明终端无数据要发,基站继续发出下一个Poll帧。

轮询中特殊情况:

在一个CFP期间,如果轮询列表中的终端没有轮询完,那么在下次CFP期间将从未轮询终端开始轮询;如果轮询列表中的终端已经轮询完,还剩有一段时间,基站将随机选择终端发出轮询帧。

轮询结束过程:基站发出End帧,表明CFP期间的结束,CP期间的开始。

下图是PCF中帧传输的一个例子。

OFDM基带设计

1 发射机总体结构

发射机的总体结构如下图所示。

发送端的处理器包括多个功能模块:训练序列生成模块,Signal符号生成模块,Data符号生成模块,IFFT处理模块,循环前缀添加与加窗处理模块,主控单元和时钟生成模块。

2 发射机Symbol生成过程

物理层发射机的数据来源于MAC层传递下来的待发送数据报文,该数据报文以字节为单位。物理层发射机接收到来自于MAC层的这些数据后,将并行数据进行并串转换,得到串行的二进制比特流。这些数据通过卷积编码器进行编码,通过截断已编码的数据比特流,编码器最终输出1/2,2/3或3/4的码率数据,这些数据将根据802.11标准中指定的交织模式进行交织,交织后的比特数据根据调试方式的不同,通过映射模块映射为BPSK,QPSK, 16QAM,64QAM星座图上的点,如下图所示。

3 扰码模块

为了防止长时间的“0”或“1”序列影响同步的建立和保持,我们在发射机这边采用扰码以避免这种数据对接收机定时的不利影响。扰码模块的OFDM实现如下图所示。

4 信道编码

在802.11标准中,主要采用卷积编码的方式。卷积码的监督码不仅与本组的信息元有关,而且还与前若干组的信息源有关,这种码的纠错能力强,不仅可以纠正随机差错,而且可以纠正突发差错。

可以通过合理的硬件方式实现1/2,2/3,3/4,5/6,7/8的码率。

5 交织

802.11标准中采用的是分组交织器,其交织深度与所采用的调制方式有关:BPSK,QPSK,16QAM和64QAM的交织深度分别为38,96,192和288个比特,每种调制方式的交织深度是通过数据子载波的数量与每个符号中比特的个数相乘而得到的。

关于交织部分的细节,在这里不做过多讨论。

未完待续......

当年设计方案就写到了这里,后续有时间我再来修正,补全。

下一篇: PLC、DCS、FCS三大控

上一篇: 一种无线多媒体终端设