发布日期:2022-10-17 点击率:43

随着数字电子技术的发展,数字电路已由早期的分立元件逐渐发展成集成电路,对电路设计的要求越来越高。尤其是可编程逻辑器件的出现,使得以硬件为载体、以计算机软件为开发环境的现代数字系统的设计方法日趋成熟。可编程逻辑器件设计灵活、功能强大、可在线修改、效率高等优点深受广大电子设计人 员青睐。目前,大多数现场可编程逻辑阵列( FPGA) 芯片是电压敏感型芯片,基于可重构CMOS-SRAM 单元结构,数据具有易失性,工作在低电压状态,易受干扰,尤其在工控、军用场合,外界电磁环境恶劣,电路耦合、空间辐射的杂波脉冲均会对FPGA 工作的稳定性产生影响。

干扰脉冲和毛刺信号是影响FPGA 稳定工作的主要因素,为了保证输入信号每变化一次,电路只做出一次正确的响应,必须对输入信号进行滤波处理。要实现信号滤波可以采用硬件滤波和软件滤波两 种方法。与硬件滤波相比,软件滤波不需要硬件电路的支持,从而可以减少元器件的使用,降低成本,更重要的是软件滤波更易于修改,所以常采用软件滤波的方法 来实现电路中的信号滤波问题。通过VHDL 语言编程实现信号滤波功能,介绍了延时滤波法和判决滤波法,并通过实验证明了上述两种滤波方法的可靠性。

1 延时滤波

延时滤波法的滤波原理是对输入信号的脉冲宽度进行鉴别,对那些与真实信号的宽度相差很大的干扰信号进行有效的抑制。具体的实现流程为在检测到输入信号的 状态发生变化后,延时一段时间T,脉冲宽度小于延时时间T 的输入信号被认为是干扰信号,将其滤除; 脉冲宽度大于延时时间T 的输入信号则被认为是真实信号,将其输出。针对不同脉冲宽度的干扰信号,可以通过设置不同的参数来实现相应的信号延时,从而达到有效滤波的目的。

1. 1 延时时间T 的确定

延时时间T 取决干扰信号的脉冲宽度T’。延时时间T 太短( T < T’) ,滤波不完整,脉冲宽度大于T 的干扰信号仍然会造成电路的误动作; 延时时间T 太长( T>>T’) ,会造成资源的浪费,降低电路的工作效率。

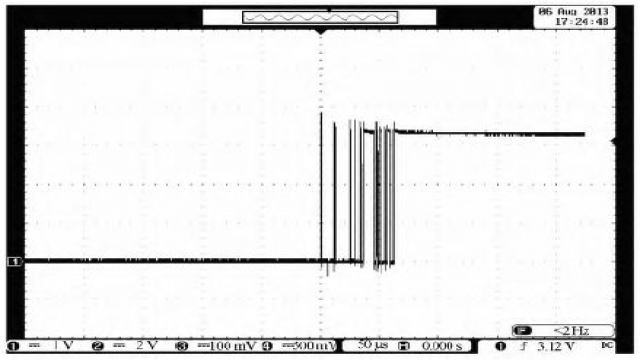

这里以某型号的扭子开关输入信号为例来介绍如何确定延时时间T。由于扭子开关的机械触点存在弹性作用,当拨动开关时,都不可避免地要在触点闭合及断开的 瞬间产生一连串的抖动。为了能够更准确地估测拨动开关时产生的干扰脉冲宽度T‘,可以用示波器对开关信号进行多次测量,经测量发现这种扭子开关信号的抖动 时间不会超过1. 5ms。图1 为没有经过滤波处理的开关信号波形。

图1 中,横坐标表示时间,每格代表50 μs,纵坐标表示电压,每格表示1 V。从图中可以明显看出,在开关信号达到稳定状态之前,有一连串的抖动,抖动时间不到1. 5 ms。这里根据实际情况,确定延时时间T = 2 ms。

1. 2 延时滤波程序设计

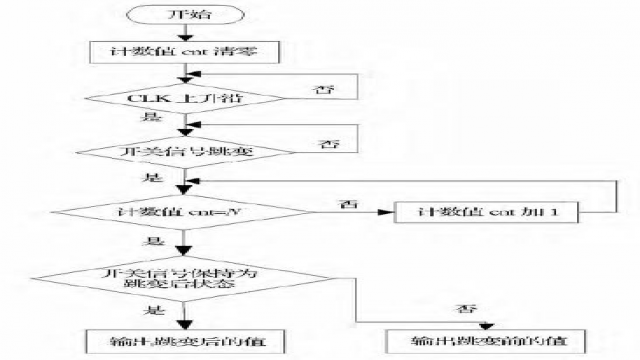

延时滤波程序采用一个计数器来实现,计数器的模值N 取决于延时时间T 和采样时钟CLK 的周期TCLK。若计数器的初始值为0 时,则N = T /TCLK -1。图2 为编写延时滤波程序的流程图。

图1 未经过滤波处理的开关信号

图2 延迟滤波程序流程图

当检测到开关信号的状态发生变化时( 这里以由‘0’变到‘1’为例) ,计数器开始计时,当计数器的计数值计到N 时,如果开关信号仍保持为变化之后的状态‘1’,则输出‘1’,否则,认为这是一个干扰脉冲,将其滤除。

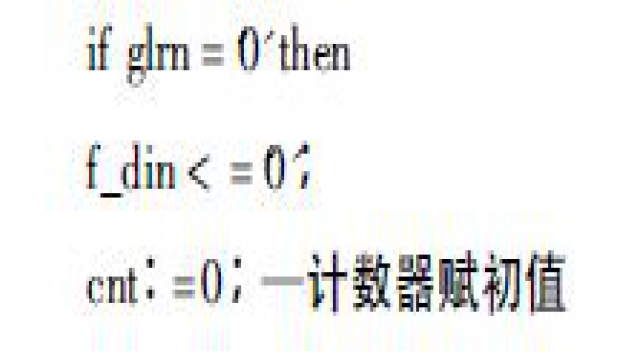

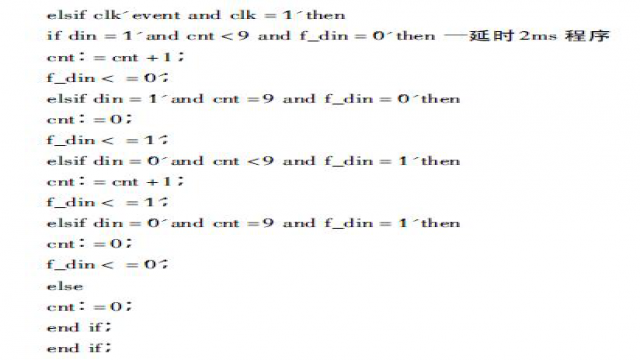

当采样时钟的频率为5 kHz 时,TCLK = 0. 2 ms,要实现2 ms 的延时时间,若计数器初始值为0,那么计数器模值N = 9。具体的VHDL 语言程序进程如下:

1. 3 延时滤波程序仿真

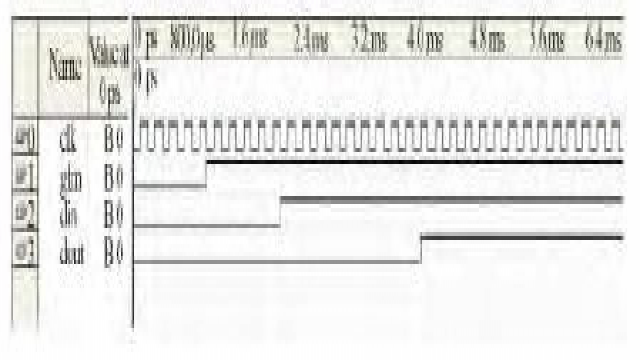

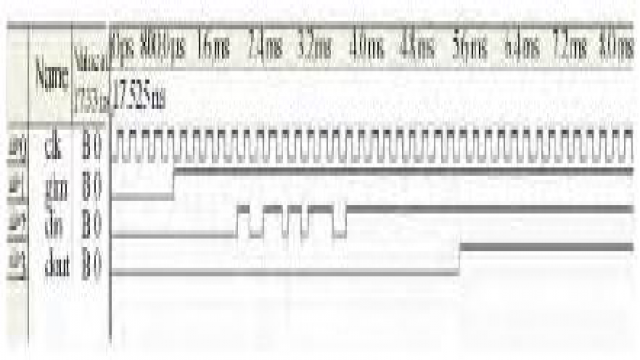

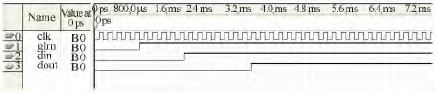

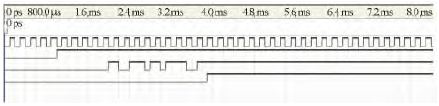

分别将开关信号din 设置成理想信号和抖动信号,利用QuartusⅡ8. 0 软件进行仿真,图3 和图4 分别为理想信号和抖动信号的延时滤波仿真波形图。

图3 理想开关信号延时滤波仿真波形

图4 抖动开关信号延时滤波仿真波形

图中clk 为采样时钟,glrn 为复位信号,din 为开关输入信号,dout 为延时滤波输出信号。从图3可以看出,从开关信号发生变化到输出发生变化的时间延时为2 ms,从图4 中可以看出,此延时滤波程序有效消除了扭子开关的抖动干扰,验证了其理论可行性。

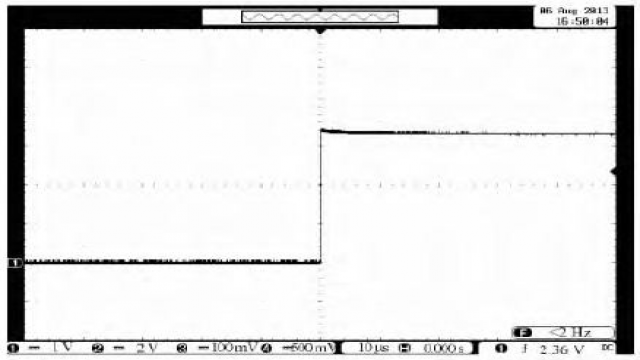

1. 4 延时滤波程序实际验证

为了验证此延时滤波程序的实际滤波效果,将其下载到Xilinx 公司的Spartan3 系列FPGA 芯片XC3S400 中,用示波器多次测量经过滤波后的开关信号,得到图5 所示的输出信号波形。图5 中,横坐标表示时间,每格代表10 μs,纵坐标表示电压,每格表示1 V。从图5 可以看出,经过滤波后的开关信号不再有抖动现象,此延时滤波程序的实际可靠性得到验证。

图5 延时滤波后的输出信号波形

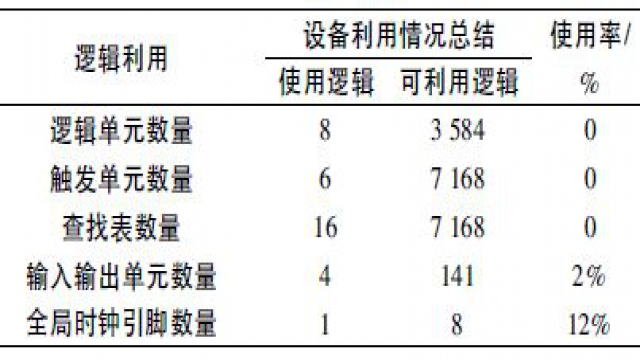

1. 5 延时滤波程序资源占用率

在电子电路的设计中,FPGA 的资源占用率是我们应该考虑的一个重要问题。如果FPGA 的资源占用率太大,会加重FPGA 的负担,影响整个电路的运行速度。表1 为延时滤波程序在XC3S400 芯片中的资源占用情况。

表1 延时滤波程序的资源占用情况

1. 6 延时滤波的特点

延时滤波比较适合对脉冲宽度已知的干扰信号进行滤波,这样可以更准确地确定延时时间,既不会因为延时时间太短而导致滤波不理想,又不会因为延时时间过长 而导致资源浪费。而且,延时程序不仅可以有效地消除开关类信号的抖动,还可以滤去干扰、噪音等其他尖峰波,抗干扰强,可靠性高。

如果电 路中存在多路输入信号时,当检测到任意一路输入信号状态发生变化时即执行延时程序,在执行延时程序的过程中将检测不到其他输入状态的变化,所以能够识别的 动作间隔不可能小于延时时间T,特别是当多路输入信号的状态集中在短时间内变化时,电路的性能会严重下降。并且,由于频繁执行延时程序,会影响系统的效率 和实时性。

2 判决滤波

判决滤波是一种基于概率统计的滤波方法。在采样时钟CLK 的控制下,每隔时间t 对开关信号进行一次采样,并对时间T0内采集到的n 个采样值进行判断( n = T0 /t) ,如果这n 个采样值中高电平‘1’的个数百分比大于X,则输出高电平; 相反,如果低电平‘0’的个数百分比大于X,则输出低电平。

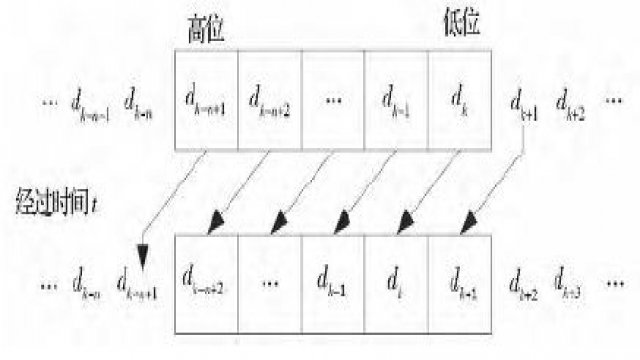

采用一个n 位寄存器来实现判决滤波,寄存器各个位的值依次为采样得到的n 个采样值。寄存器的模型如图6 所示。

图6 寄存器模型

在图6 中,n 个格子分别代表寄存器的n 个位,寄存器左侧的数据为已经处理过的数据,寄存器内的n 个数据为正在处理的数据,寄存器右侧的数据为即将处理的数据。每过一个采样时间间隔t,数据依次向高位滑动一位,最低位赋值为输入信号当前的状态值。

如上述过程,寄存器内的数据在不断地更新,数据每滑动一次,即对n 个采样值进行一次判断,从而达到滤波的目的。由于干扰脉冲的随机性,采到高电平和低电平的概率是相等的,所以,作为判断依据的百分比X 不能小于50%。在实际应用中,为了使滤波更可靠,X 的取值一般都大于50%。

2. 1 判决滤波程序设计

本设计采用一个9 位寄存器( n = 9) ,每次判断时只要‘1’的个数大于或等于5,则滤波输出‘1’,否则输出‘0’( X = 5 /9) 。图7 为判决滤波程序的流程图。

图7 判决滤波程序流程图

主要的程序进程如下:

2. 2 判决滤波程序仿真

同样以开关信号为例,在QuartusⅡ8. 0 软件中仿真来验证结果。图8 和图9 分别为对理想开关信号和抖动开关信号进行判决滤波的仿真波形图。

图8 理想开关信号判决滤波仿真波形

图9 抖动开关信号判决滤波仿真波形

仿真结果显示,此判决滤波程序也可以实现滤波目的。对比图4 和图9 可以发现,对相同的抖动脉冲进行滤波,虽然两种滤波方法都能有效滤除抖动,但是滤波效果是不同的,判决滤波的实时性比较好。

2. 3 判决滤波程序实际验证

将此判决滤波程序同样下载到XC3S400 芯片中去,用示波器多次测量,得到滤波后的开关输出信号波形如图10 所示。

图10 判决滤波后的输出信号波形

图10 中,横坐标表示时间,每格代表5 μs,纵坐标表示电压,每格表示1 V。从图中可以看出,开关信号中的抖动脉冲已被完全滤除,证明此判决滤波程序是实际可行的。

2. 4 判决滤波的特点

判决滤波既可以用来对开关信号这类抖动时间已知的信号进行滤波,也可以对脉宽很窄的干扰信号进行滤波。在高速电路中,系统晶振常常在几十兆赫兹左右,时 钟宽度单位达到纳秒级,这可以使判决滤波的采样时间间隔t 达到纳秒级,即寄存器的各个位可在几十纳秒内重新赋值,从而达到消除窄脉冲干扰信号的目的。

2. 5 判决滤波程序的资源占用率

判决滤波程序在XC3S400 芯片中的资源占用情况如表2 所示。

表2 判决滤波程序的资源占用情况

对比表1 显示的数据来看,两种滤波方法的资源占用率都比较小,相对延时滤波程序而言判决滤波程序的资源占用率稍大一些。

3 结论

实验证明延时滤波和判决滤波均能达到很好的滤波效果,在电路的设计过程中,可以根据干扰信号的类型选择合适的滤波方法。在实时性要求不是很高、干扰信号 脉冲宽度可估测的电路中,可以采用延时滤波法,既节省资源又能有效滤除干扰信号; 在实时性要求比较高、运行速度比较快、干扰信号脉冲宽度很窄的电路中,可以采用判决滤波法,既能有效滤波又能保证电路的效率。

下一篇: PLC、DCS、FCS三大控

上一篇: 直流PTC热敏电阻恒温