发布日期:2022-10-18 点击率:39

本文回顾了Serdes的发展历程,提出了Serdes技术分代及其特点,讲述当前国内外Serdes的技术现状,以及Serdes技术的发展趋势,对Serdes架构和各模块技术演变、关键技术挑战进行了分析,并从协议、电路设计、信号完整性、发展趋势几个维度加以详细讨论。

Serdes是英文单词串行器(Serializer)和解串行器(De-Serializer)的合成词,可以称之为串行解串器。根据其功能来讲,Serdes就是在发送端将并行数据转换为串行数据,在接收端将串行数据恢复为并行数据的电路。

目前,Serdes技术在有线通信方面已经得到了广泛应用。按照应用连接的类型,主要分为芯片与光模块的互联;芯片与芯片的互联;以及以太网互连。

以太网接口主要有10BASE-T、10BASE-F、100BASE-T、10BASE-FX、1000BASE-X、1000BASE-T接口,在跨城市互联中将主要用到GE及以上的接口。GE物理接口有1000BASE-X(802.3z标准)和1000BASE-T(802.3ab标准)两种。未来的高速率接口(100G或以上)均为GE类型,为了与100GE兼容,OTU4标准的制定为100GE,高端路由器厂家目前均可提供100GE,并大部分计划开发100GE OTN接口 。可以预见的是未来的高速端口将是以太网和OTN这两种类型。

在以并行通信主导的内存颗粒的访问接口领域,也有分别是海力士和AMD主导的HBM(High BandwidthMemory,高带宽存储器)以及Intel支持、美光主导的HMC(Hybrid Memory Cube)等串行接口,作为与DDR5不同的一种演进方向。

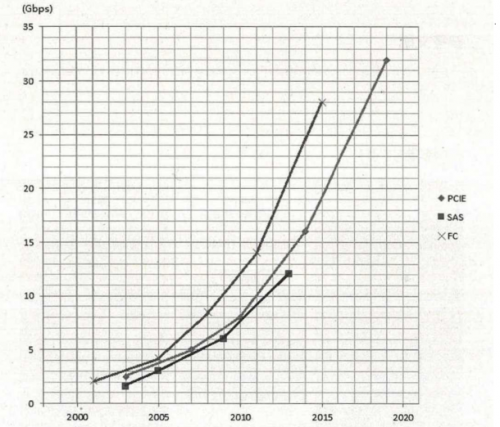

由此我们可以看到,Serdes已经跟随通信协议,广泛应用在电信、IT和个人消费电子领域。并且随着通信容量的快速提升,各种通信协议的单通道数据率也快速提升,例如图1所示的几种协议演进。

图1:部分协议的单通道数据率

1 技术现状

目前,国际上最先进的Serdes单通道为64~128 Gbit/s之间。在功耗方面,除了单通道最大功耗(mW)外,由于电路功耗跟工作的数据率强相关,所以通常也使用每bit消耗的功耗(pJ/b)来衡量。在ISSCC 2019会议上,IBM发表的单通道128 Gbit/s 1.3 pJ/b的发送器和100 Gbit/s 1.1 pJ/b的接收器,基本代表了当前国际Serdes技术的最高水平 。

令人注意的是,华为旗下的海思半导体在Serdes领域也有相当先进的技术,已经形成了从45 nm~7 nm工艺,10 Gbit/s~64 Gbit/s的多款IP核,并在近百款芯片中商用。在2018年和2019年的ISSCC会议上,华为加拿大研究所先后发表了基于台积电16 nm 64 Gbit/s和7 nm 60 Gbit/s的Serdes,并且接近商用,代表着国产Serdes技术的最高水平 。

另外,清华大学、北京大学、东南大学等院校在Serdes领域研究也取得了很大的进步,有多篇32Gbit/s、40Gbit/s、50Gbit/s的学术成果 。

2 发展历程

Serdes技术的发展,依本文作者观点,可以分为以下几个阶段。

一个完整的Serdes系统,包括参考时钟,PLL,上层协议,编解码,发送端(Transmitter,TX),信道,接收端(RX)等部分组成。其中有源器件主要是芯片本身如Serdes的收发端,外部的ESD防护器件,光模块等;无源器件包括单板、背板及走线,AC耦合电容连接器,背板,SMA头,线缆等。

下面,我们进一步从这些方面讨论Serdes的发展趋势和挑战。

3 协议

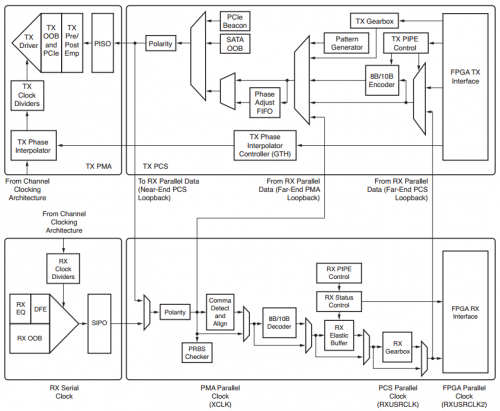

Serdes通常作为通信协议的物理层的物理介质(PMA)子层部分,由此要严格准从协议规定。Serdes作为一个芯片的底层模块,除了满足单一的通信协议数据率越来越高的挑战,基于成本等考虑,通常还要求同一个Serdes IP核能够兼容多种协议。

从Serdes设计的角度,常见的通信协议可以分为几大类别。

4 锁相环

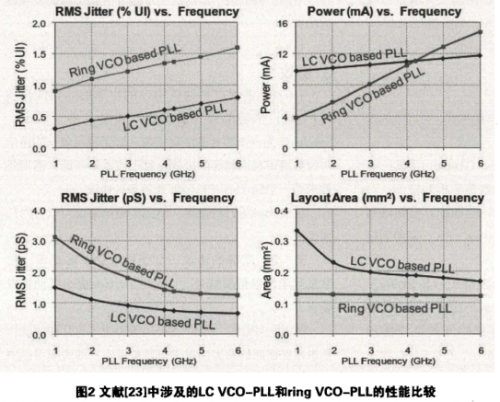

常见的锁相环通常基于LC振荡器(LC VCO)或者环形振荡器(Ring VCO)结构。

环形振荡器易集成、面积小、且容易产生多相位的时钟。LC振荡器的电感占用芯片面积较大,设计难度较高,优点是相噪性能更好。但是随着Serdes数据率的提高,电感越小谐振频率越高,所以电感占用面积大的缺点有所缓解。反而是环形振荡器PLL的功耗、相噪等问题,无法满足更高的要求。但是随着Serdes对PLL频率、相噪、功耗等提出了越来越高的要求。在10 Gbps以上的Serdes设计中,通常会使用基于LC VCO的PLL,以获得更好的相噪水平。

从LC VCO-PLL和ring VCO-PLL的性能比较我们可以看出:LC VCO-PLL在抖动方面具有较大优势,在约(4~5)GHz以下的低频应用时,ring VCO-PLL在功耗和面积上有一定优势。但随着频率的更加,ringVCO需要更大的电流来提高振荡频率,LC VCO占最大面积的电感和电容器件将更小,所以功耗和面积缺点不再那么突出了。

一般来说,在5~8 GHz以下的应用中,基于ringVCO的PLL是可行的。如果在更高的频率,基于LCVCO的PLL更为合适。

5 发送端

发送端主要功能包括如下。

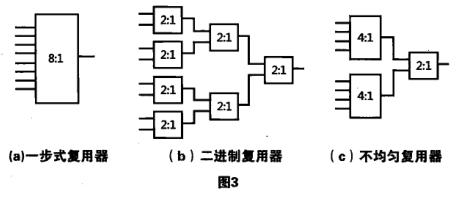

串行器的核心是多路复用器电路,常见的有3类:一步式的多路复用器,二进制的多路复用器,多种复用器组合不均匀串行器,如图3所示。

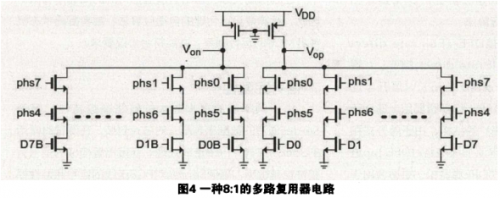

一种8:1的多路复用器如图4所示。Phs0~Phs7是同频率但等相位差的时钟,只有在Phs7和Phs4同时为高时,数据D7B和D7才能被送出;只有在Phs0和Phs5同时为高时,数据D0B和D0才能被送出,依次类推。

循环的等相位差时钟,将数据D0~D7和D0B ~D7B依次串行高速输出,即可达到并行转串行的目的。此类结构优点在于电路简单,缺点是难以应用在数据位宽较宽的场景。而且在高速并串转换时,对时钟相位的抖动等要求很高,而变得难以实现。也就是说,一步式复用器的最高工作速率低于二进制复用器,所以一步式复用器一般应用在低速Serdes并串转换电路中,或者作为不均匀串行器的第1级。

不均匀复用器,既可以灵活配置位宽,也避免了一步式复用器对多相时钟的高指标要求,并且比二级制复用器更高效,因此是一种很适合高速串行器的结构。

发送端的驱动端电路,常见的是CML和SST结构。

CML结构本身方便电流叠加,所以很容易实现预加重功能。但是输出摆幅与输出阻抗和驱动电流的乘积相关,输出阻抗通常又被限制在50~100 Ω,因此要获得大摆幅就必须使用较大的驱动电流,使得功耗居高不下。这在功耗问题日益突出的今天,已经变得无法接受。

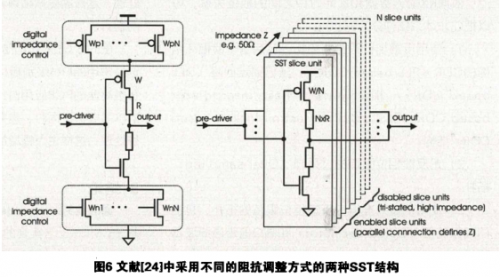

文献中的两种不同阻抗调整方式的SST结构如图所示,SST结构的输出摆幅与其电源电压直接相关,一般来说产生同样摆幅,SST结构的功耗只有CML结构的1/4左右,因此在10 Gbps以上的Serdes中越来越受到青睐。

但是SST结构的预加重信号叠加相比CML结构更为复杂。使问题更加困难的是,采用并联SST等结构来实现预加重功能时,由于开关的MOS管数量不同,阻抗匹配难以保证。因此,通常需要阻抗校准电路和状态机来保证初始化时,Serdes 发送端的阻抗能够匹配在差分100 Ω左右。

6 接收端

信道的插损与信号频率成正比,频率越高衰减越大。所以随着Serdes数据率提升,信道的衰减也越来越严重。为了补偿信道的衰减,通常需要在发送端预加重功能和接收端均衡功能。接收端的均衡器一般由CTLE和DFE构成。CTLE和DFE已经广泛应用于当前的Serdes架构中。

RX设计面临的几个挑战是:更优的DFE拓扑和CDR拓扑,以及更优的自适应算法。

DFE架构经历了全速直接DFE(Full rate directDFE)、半速直接DFE(Half rate direct DFE)、展开全速DFE(Full rate unrolled DFE)、展开半速DFE(Unrolled half rate DFE)和多路复用半速DFE(Multiplexed half rateDFE)等结构。由于展开式和多路复用等结构,不用通过电流加法电路对DFE tap进行求和,而使得时序比直接式DFE更宽松,更适合用于解决速率提升带来的时序紧张问题。

根据RX输入数据和本地时钟之间的相位关系,可以把CDR体系结构分为3类。

也可根据应用场景将CDR分为突发模式和连续模式的CDR。突发模式系统通常用于点对多点应用中,不同的发送方在突发之间传输具有静默时间间隔的包数据。

每当请求传输数据包时,数据传输链路被重新激活,并且在其他时间保持不活动状态,如以太网无源光网络(EPON)、千兆无源光网络(GPON)等。突发模式CDR结构一般采用无反馈相位跟踪的拓扑结构,如门控振荡器和过采样技术。基于相位插值器的CDR不存在抖动峰值或稳定性问题,具有无限的相位捕获范围,但存在量化误差。

因此,需要根据芯片不同的应用场景来选择最佳的Serdes CDR结构。

自适应算法可以由数字逻辑状态机来执行,也可以固件的形式烧录在片上MCU中执行。例如PCIE等协议在速率切换时,要求24 ms以内达到规定的误码率以下,否则协商失败,留给自适应执行的时间非常有限。

因此,就需要设计合理的自适应算法,或者提高状态机或者MCU的运行频率,才能符合协议要求。

7 信号完整性

由于频率越高插损越大的链路参数特性,随着Serdes通道的数据率越高,对芯片封装、在测试时常用的Socket夹具、PCB走线处理、连接器等构成的信号完整性也越敏感。高速Serdes对PCB走线的信号完整性提出了越来越严苛的要求,例如PCB板材的选取,过孔的处理,是否需要背钻等等,都是信号完整性所要考虑的问题。

在5~8 Gbit/s以下的Serdes单板PCB设计时,一般选择常用的FR4级别板材就能满足信号完整性的要求;在更高速的PCB应用时,则要考虑M4、M6或者同级别的PCB板材。同时,需要对过孔进行埋孔、背钻等做特殊处理,这样也大幅增加了投板成本。

8 结论

通信业务对于Serdes数据率的需求日益增长,当前基于CMOS工艺实现的Serdes最高单通道数据率已经达到128 bit/s,无论对于CMOS电路设计还是链路信号完整性,单通道数据率的进一步提高已经变得越来越困难。与此同时,很多系统应用对Serdes的功耗的还有苛刻的要求,也是设计人员面临的巨大挑战之一。

硅光子技术可以基于硅和硅衬底材料,利用CMOS制程将电信号转换为光信号传输。光替代链路的铜线,可以得到很好的传输数据率和极低的损耗。如果硅光子技术获得突破和成熟,加上单板的光走线,可以实现芯片与芯片之间的光互联,那么,Serdes技术的侧重点会变得很大的不同,将对驱动能力要求大大的降低。因此,硅光子技术是一种极具可能性的演进方向 。(参考文献略)

来源:电子产品世界

下一篇: PLC、DCS、FCS三大控

上一篇: 小基站助力5G连接