发布日期:2022-10-09 点击率:59

l 引言

与传统模拟示波器相比.数字存储示波器不仅具有可存储波形、体积小、功耗低,使用方便等优点,而且还具有强大的信号实时处理分析功能。在电子测量领域,数字存储示波器正在逐渐取代模拟示波器。但目前我国使用高性能数字存储示波器主要依靠国外产品,而且价格昂贵。因此研究数字存储示波器具有重要价值。借于此,提出了一种简易数字存储示波器的设计方案,经测试,性能优良。

2 数字存储示波器基本工作原理

数字存储示波器与模拟示波器不同在于信号进入示波器后立刻通过高速A/D转换器将模拟信号前端快速采样,存储其数字化信号。并利用数字信号处理技术对所存储的数据进行实时快速处理,得到信号的波形及其参数,并由示波器显示,从而实现模拟示波器功能,而且测量精度高。还可存储信号,因而,数字存储示波器可以存储和调用显示特定时刻信号。

3 系统分析论证

3.1 A/D实时采样

根据奈奎斯特采样定理,采样速率必须高于2倍的信号最高频率分量。对于正弦信号,一周期内应有2个采样点。为了不失真恢复被测信号,通常一周期内需要采样8个点以上。为了配合高速模数转换器,采用FPGA控制M/D转换器的采样速率,以实现高速实时采样。实时采样可以实现整个频段的全速采样,本系统设计选用ADI公司的12位高速A/D转换器AD9220,其最高采样速率可达10 MHz。

3.2 双踪显示

本系统设计的双踪显示模块是以高速切换模拟开关选通两路信号进入采样电路,两路波形存储在同一个存储器的奇、偶地址位。双踪显示时,先扫描奇地址数据位,再扫描偶地址数据位。采用模拟开关代替一个模数转换器,避免两片高速A/D转换器相互干扰,降低系统调试难度,并且实现系统功能。

3.3 触发方式

采用FPGA内部软件触发方式,通过软件设置触发电平,所设置的施密特触发器参数易于修改,从而抑制比较器产生的毛刺。当采样值大于触发电平,则产生一次触发。该方式充分利用了FPGA的资源,减少外围电路,消除硬件毛刺产生的干扰,易于调整触发电压。

3.4 波形显示位置的调节

3.4.1 行扫描调节

通过控制FPGA内部双口RAM(1 KB)的起始地址的偏移量确定来控制波形的移动。其具体方法是将滑动变阻器R上的电平通过模数转换器转换为数字信号传输给FPGA,再与初始电平数字信号(显示位置复位时,滑动变阻器R的电平采样值)相比较决定起始地址ADR0的偏移量。该方法可易于实现波形满屏和自动显示功能。

3.4.2 列扫描调节

MAXl97采样A、B通道的Position电位器值,所得采样值经FPGA送至16位串行D/A转换器,MAX542产生直流电平,该直流电平与列扫描波形相加送至模拟示波器显示,实现波形上下移动。为分离A、B通道,在读A通道波形数据时,FPGA必须将Position A电位器的值送至D/A转换器;而在读B通道波形数据时,也必须将Position B电位器的值送至D/A转换器,这样可在调节某一电位器时,实现相应通道波形上下移动。

3.5 波形数据存储

数字示波器存储波形数据可采用外接的双口RAM或通用静态RAM,同时FPGA可控制RAM的地址线,从而实现波形数据的存储。双口RAM可同时进行读写操作,由于本系统设计采用FPGA,因此可充分利用FPGA的逻辑阵列和嵌入式阵列,可将双口RAM写入FPGA内部,从而无需外接RAM,减少硬件电路,提高简易数字示波器的可靠性。

4 系统设计方案

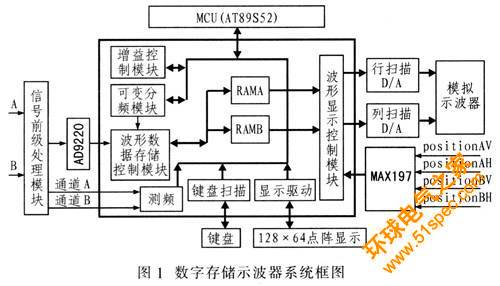

本系统设计框图如图1所示。整个系统是以FPGA为核心,包括前端模拟信号处理模块、单片机模块、显示模块和键盘输入模块。而信号的前级处理模块又包括射级跟随器、程控放大电路、整形电路。A、B通道的信号经前级处理变为O~4 V,AD9220对其采样。波形存储控制模块将其采样数据写入FPGA内部RAM,再由波形显示控制模块进行显示。FPGA通过编程设置实现测频、键盘扫描、显示驱动、波形存储控制等功能。单片机AT89S52控制整个系统键盘和点阵液晶模块实现人机交互。通过面板按键可方便调整波形显示方式。

5 硬件电路设计

5.1 程控放大电路

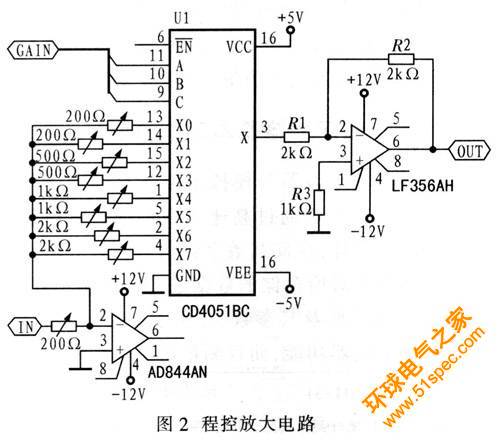

采用模拟开关CD4051、宽带运算放大器AD844及精密电位器实现10 mV/div~2 V/div的多档垂直分辨率。FPGA含有通道选择寄存器模块,通过单片机写入通道号控制模拟开关以选通不同的反馈电阻,实现不同放大倍数,将信号调理在满足AD9220的0~4 V的范围内,具体电路如图2所示。

5.2 数据采集模块

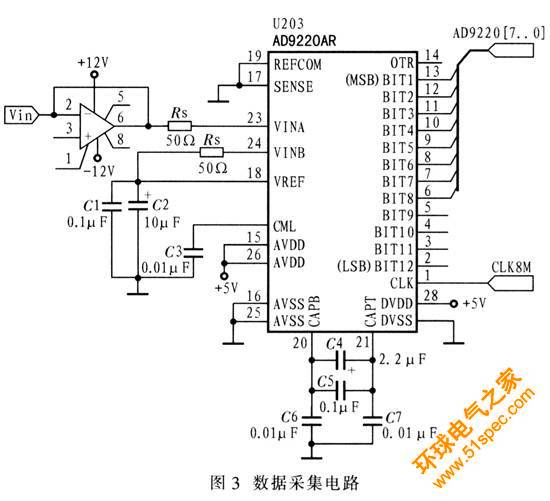

本系统设计采用ADI公司的高速模数转换器AD9220实现波形信号的采集,AD9220最高采样速率可达10 MHz,采用外部晶体振荡器8 MHz,FPGA内部通过采样实现波形存储。AD9220有直流耦合和交流耦合两种输入方式。本系统设计采用直流耦合,0~5 V的输入方式。采用内部2.5 V参考电压。由于系统垂直分辨率只需255级,故采用AD9220的高8位。数据采集电路如图3所示。

5.3 FPGA设计

系统采用Verilog HDL语言,在QuartusII软件下对FPGA进行逻辑电路的描述编程,可灵活实现系统所需电路和控制模块。

5.3.1 触发模块

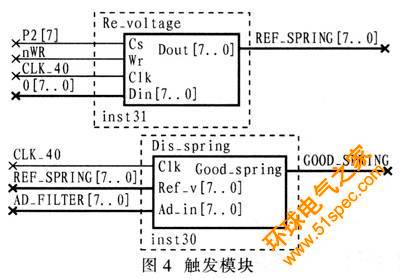

单片机先向FPGA模块写入设置的触发电压,FPGA内部相比较后,当采样值大于该触发电压时,则产生一次触发。图4为触发模块。

5.3.2 程控放大控制模块

单片机首先以100 mv/div的档位对信号采样,通过比较与该信号最近的模拟开关的通道号,然后写入控制字,产生相应通道号,实现垂直分辨率的调整。

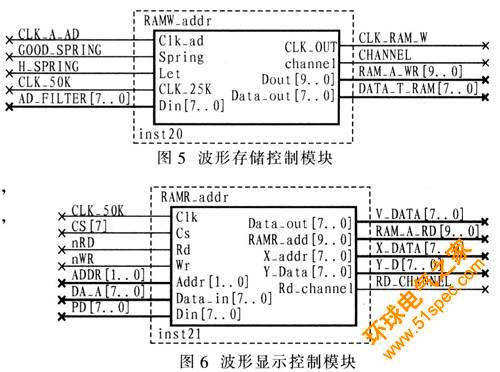

5.3.3 波形存储控制模块

该模块为RAM模块的写地址累加器,可控制波形的存储。H_sering为单次和多次触发控制引脚,当为高电平时,单次触发,停止向RAM写入数据,所显示波形为存储波形;为低电平时,多次触发,当检测到一次触发时,即向RAM写一次数据,共l K个点,并在写操作时屏蔽触发。写地址先写奇地址,存入通道一采样后的波形数据,后写偶地址,存入通道二采样后的波形数据。如果连续多次检测不到触发时,向RAM中写入全0,显示一条直线,即实现自动捕捉功能。波形存储控制模块如图5所示。

5.3.4 波形显示控制模块

该模块为读地址累加器,从RAM中读取数据,并产生行扫描和列扫描数据。通过单片机写入累加器基地址,改变读取数据的起始位,实现波形的平移。该模块还可计算波形的峰峰值、平均值,单片机可直接读回数值。波形显示控制模块如图6所示。

6 系统软件设计

系统软件设计实现人机交互、信息提示、系统启动与复位等功能。首先系统初始化,显示默认通道波形,再等待按键按下。当按键按下后,完成相应功能,显示相应波形,然后循环等待。系统软件设计流程如图7所示。

7 测试结果

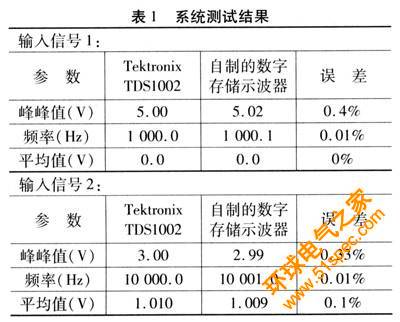

使用自制的数字存储示波器和tektronix TDSl002型数字示波器测量输入信号,其中部分测量数据如表1所列。

通过对比测试和结果分析,各种输入信号在自制数字存储示波器上可精确显示波形,并且实现波形的双踪显示及波形水平、垂直平移,频率、平均值、峰峰值的测量,误差小,达到一定的精度要求。

8 结语

本系统设计采用单片机作为核心控制器,充分利用FPGA的可编程逻辑功能,完成相关电路设计。软硬件有机结合实现简易数字存储示波器的设计,系统总体功能完善,稳定性高,使用方便。

下一篇: 断路器、隔离开关、接

上一篇: 索尔维全系列Solef?PV

型号:A-CCS 084-Z-T

价格:面议

库存:10

订货号:A-CCS 084-Z-T

型号:WPLCC084-1PTRC

价格:面议

库存:10

订货号:WPLCC084-1PTRC

型号:WPLCC020-ST1RC

价格:面议

库存:10

订货号:WPLCC020-ST1RC

型号:IC120-0684-304

价格:面议

库存:10

订货号:IC120-0684-304

型号:WPLCC052-1PTRC

价格:面议

库存:10

订货号:WPLCC052-1PTRC

型号:A-CCS 044-Z-SM

价格:面议

库存:10

订货号:A-CCS 044-Z-SM